## INTEGRATED CIRCUITS

# DATA SHEET

## **PCK2023**

CK408 (66/100/133/200 MHz) spread spectrum differential system clock generator

Product data Supersedes data of 2001 Sep 07

## CK408 (66/100/133/200 MHz) spread spectrum differential system clock generator

**PCK2023**

#### **FEATURES**

- 3.3 V operation

- Three differential CPU clock pairs

- Ten PCI clocks at 3.3 V

- Six 66 MHz clocks at 3.3 V

- Two 48 MHz clocks at 3.3 V

- One 14.318 MHz reference clock

- 66,100, 133 or 200 MHz operation

- Power management control pins

- CPU clock skew less than 200 ps cycle-to-cycle

- CPU clock skew less than 150 ps pin-to-pin

- 1.5 ns to 3.5 ns delay on PCI pins

- Spread Spectrum capability

#### **DESCRIPTION**

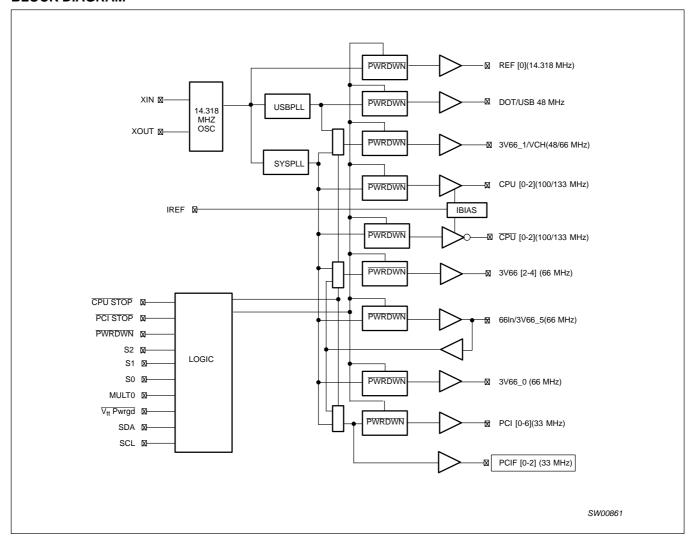

The PCK2023 is a clock synthesizer/driver for a Pentium IV and other similar processors.

The PCK2023 has three differential pair CPU current source outputs. There are ten PCI clock outputs running at 33 MHz and two 48 MHz clocks. There are six 3V66 outputs. Finally, there is one 3.3 V reference clock at 14.318 MHz. All clock outputs meet Intel's drive strength, rise/fall times, jitter, accuracy, and skew requirements.

The part possesses a dedicated power-down input pin for power management control. This input is synchronized on-chip and ensures glitch-free output transitions.

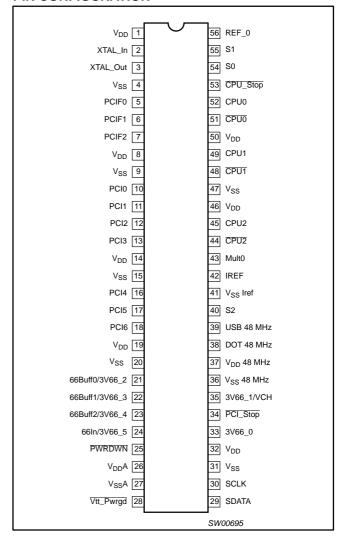

### **PIN CONFIGURATION**

### ORDERING INFORMATION

| PACKAGES             | TEMPERATURE RANGE | ORDER CODE | DRAWING NUMBER |

|----------------------|-------------------|------------|----------------|

| 56-Pin Plastic SSOP  | 0 to +70 °C       | PCK2023DL  | SOT371-1       |

| 56-Pin Plastic TSSOP | 0 to +70 °C       | PCK2023DGG | SOT364-1       |

Intel and Pentium are registered trademarks of Intel Corporation.

2003 Jul 31 2

# CK408 (66/100/133/200 MHz) spread spectrum differential system clock generator

PCK2023

### **PIN DESCRIPTION**

| PIN NUMBER                      | SYMBOL                    | FUNCTION                                                                                                                                   |

|---------------------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 56                              | ref                       | 3.3 V 14.318 MHz clock output.                                                                                                             |

| 2                               | XTAL_In                   | 14.318 MHz crystal input.                                                                                                                  |

| 3                               | XTAL_Out                  | 14.318 MHz crystal output.                                                                                                                 |

| 44, 45, 48, 49, 51, 52          | CPU & <u>CPU</u><br>[2:0] | Differential CPU clock outputs.                                                                                                            |

| 33                              | 3V66_0                    | 3.3 V 66 MHz clock output.                                                                                                                 |

| 35                              | 3V66_1/VCH                | 3.3 V selectable through I <sup>2</sup> C to be 66 MHz or 48 MHz                                                                           |

| 24                              | 66ln/3V66_5               | 66 MHz input to buffered 66Buff and PCI or 66 MHz clock from internal VCO.                                                                 |

| 21, 22, 23                      | 66Buff [2:0] / 3V66 [4:2] | 66 MHz buffered outputs from 66 input or 66 MHz clocks from internal VCO.                                                                  |

| 5, 6, 7                         | PCIF<br>[2:0]             | 33 MHz clocks divided down from 66 input or divided down from 3V66.                                                                        |

| 10, 11, 12, 13, 16, 17,<br>18   | PCI<br>[6:0]              | PCI clock outputs divided down from 66 input or divided down from 3V66.                                                                    |

| 39                              | USB                       | Fixed 48 MHz clock output.                                                                                                                 |

| 38                              | DOT                       | Fixed 48 MHz clock output.                                                                                                                 |

| 40                              | S2                        | Special 3.3 V 3 level input for mode selection.                                                                                            |

| 54, 55                          | S1, S0                    | 3.3 V LVTTL inputs for CPU frequency selection.                                                                                            |

| 42                              | I <sub>ref</sub>          | A precision resistor is attached to this pin which is connected to the internal current reference.                                         |

| 43                              | Mult0                     | 3.3 V LVTTL input for selecting the current multiplier for the CPU outputs.                                                                |

| 25                              | PWRDWN                    | 3.3 V LVTTL input for PowerDown active low.                                                                                                |

| 34                              | PCI_Stop                  | 3.3 V LVTTL input for PCI_Stop active low.                                                                                                 |

| 53                              | CPU_Stop                  | 3.3 V LVTTL input for CPU_Stop active low.                                                                                                 |

| 28                              | Vtt_Pwrgd                 | 3.3 V LVTTL input is a level sensitive strobe used to determine when S [2:0] and Mult0 inputs are valid and ok to be sampled (active low). |

| 29                              | SDATA                     | I <sup>2</sup> C compatible SDATA.                                                                                                         |

| 30                              | SCLOCK                    | I <sup>2</sup> C compatible SCLOCK.                                                                                                        |

| 1, 8, 14, 19, 32, 37, 46,<br>50 | V <sub>DD</sub>           | 3.3 V power supply for outputs.                                                                                                            |

| 26                              | V <sub>DD</sub> A         | 3.3 V power supply for PLL.                                                                                                                |

| 4, 9, 15, 20, 31, 36, 41,<br>47 | V <sub>SS</sub>           | Ground for outputs.                                                                                                                        |

| 27                              | V <sub>SS</sub> A         | Ground for PLL.                                                                                                                            |

3

### **BLOCK DIAGRAM**

## CK408 (66/100/133/200 MHz) spread spectrum differential system clock generator

PCK2023

### FREQUENCY SELECT/FUNCTION TABLE

| S2  | S1 | S0 | CPU     | 3V66   | 66BUFF/<br>3V66 | 66ln/<br>3V66_5 | PCIF/PCI | REF 0      | USB/DOT | 3V66_1/<br>VCH |

|-----|----|----|---------|--------|-----------------|-----------------|----------|------------|---------|----------------|

| 1   | 0  | 0  | 66 MHz  | 66 MHz | 66 In           | 66 input        | 66 ln/2  | 14.318 MHz | 48 MHz  | 66/48 MHz      |

| 1   | 0  | 1  | 100 MHz | 66 MHz | 66 In           | 66 input        | 66 ln/2  | 14.318 MHz | 48 MHz  | 66/48 MHz      |

| 1   | 1  | 0  | 200 MHz | 66 MHz | 66 In           | 66 input        | 66 ln/2  | 14.318 MHz | 48 MHz  | 66/48 MHz      |

| 1   | 1  | 1  | 133 MHz | 66 MHz | 66 In           | 66 input        | 66 ln/2  | 14.318 MHz | 48 MHz  | 66/48 MHz      |

| 0   | 0  | 0  | 66 MHz  | 66 MHz | 66 MHz          | 66 MHz          | 33 MHz   | 14.318 MHz | 48 MHz  | 66/48 MHz      |

| 0   | 0  | 1  | 100 MHz | 66 MHz | 66 MHz          | 66 MHz          | 33 MHz   | 14.318 MHz | 48 MHz  | 66/48 MHz      |

| 0   | 1  | 0  | 200 MHz | 66 MHz | 66 MHz          | 66 MHz          | 33 MHz   | 14.318 MHz | 48 MHz  | 66/48 MHz      |

| 0   | 1  | 1  | 133 MHz | 66 MHz | 66 MHz          | 66 MHz          | 33 MHz   | 14.318 MHz | 48 MHz  | 66/48 MHz      |

| Mid | 0  | 0  | Low     | Hi Z   | Hi Z            | Hi Z            | Hi Z     | Hi Z       | Hi Z    | Hi-Z           |

| Mid | 0  | 1  | Tclk/2  | Tclk/4 | Tclk/4          | Tclk/4          | Tclk/8   | Tclk       | Tclk/2  | Tclk/4         |

#### NOTE:

- 1. Mid is defined as a voltage level between 1.0 V and 1.8 V for 3 level input functionality. LOW is below 0.8 V. HIGH is above 2.0 V.

- 3V66\_1/VCH output frequency is set by the I<sup>2</sup>C.

Frequency of the 48 MHz outputs must be +167 ppm to match USB default.

- 4. Rref output min = 14.316 MHz, nominal = 14.31818, max = 14.32 MHz.

- 5. Tclk is a test clock over-driven on the XTAL\_In input during test mode.

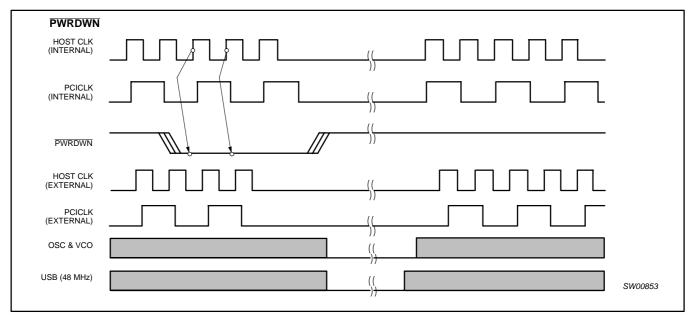

### **POWER DOWN MODE**

| PWRDWN | CPU                 | CPU    | 3V66   | 66BUFF/<br>3V66 | 66ln/<br>3V66_5 | PCIF/PCI | REF 0  | USB/DOT | 3V66_1/<br>VCH |

|--------|---------------------|--------|--------|-----------------|-----------------|----------|--------|---------|----------------|

| 1      | Normal              | Normal | Normal | Normal          | Normal          | Normal   | Normal | Normal  | Normal         |

| 0      | I <sub>ref</sub> *2 | Float  | LOW    | LOW             | LOW             | LOW      | LOW    | LOW     | LOW            |

### **HOST SWING SELECT FUNCTIONS - CK408**

| MULT 0 | BOARD<br>IMPEDANCE | I <sub>ref</sub>                                    | Іон                  | V <sub>OH</sub> @ 50 W |

|--------|--------------------|-----------------------------------------------------|----------------------|------------------------|

| 0      | 50 Ω               | $R_{ref} = 221.1\%$<br>$I_{ref} = 5.00 \text{ mA}$  | $I_{OH} = 4*I_{ref}$ | 1.0 V                  |

| 1      | 50 Ω               | $R_{ref} = 475.1\%$<br>I $_{ref} = 2.32 \text{ mA}$ | $I_{OH} = 6*I_{ref}$ | 0.7 V                  |

|                  | CONDITIONS                       | CONFIGURATION                     | LOAD                                      | MIN.                                       | MAX.                                       |

|------------------|----------------------------------|-----------------------------------|-------------------------------------------|--------------------------------------------|--------------------------------------------|

| l <sub>OUT</sub> | V <sub>DD</sub> = 3.3 V          | All combinations, see Table above | Nominal test load for given configuration | -7% of I <sub>OH</sub><br>See Table above  | +7% of I <sub>OH</sub><br>See Table above  |

| l <sub>OUT</sub> | $V_{DD} = 3.3 \text{ V} \pm 5\%$ | All combinations, see Table above | Nominal test load for given configuration | -12% of I <sub>OH</sub><br>See Table above | +12% of I <sub>OH</sub><br>See Table above |

5

## CK408 (66/100/133/200 MHz) spread spectrum differential system clock generator

PCK2023

### **ABSOLUTE MAXIMUM RATINGS<sup>1, 2</sup>**

| SYMBOL           | PARAMETER                                                  | CONDITION                                                                       | L    | LIMITS                |      |  |

|------------------|------------------------------------------------------------|---------------------------------------------------------------------------------|------|-----------------------|------|--|

| STIVIBUL         | PARAMETER                                                  | CONDITION                                                                       | MIN  | MAX                   | UNIT |  |

| $V_{DD3}$        | DC 3.3 V supply                                            |                                                                                 | -0.5 | +4.6                  | V    |  |

| I <sub>IK</sub>  | DC input diode current                                     | V <sub>I</sub> < 0                                                              | _    | -50                   | mA   |  |

| VI               | DC input voltage                                           | Note 2                                                                          | _    | _                     | V    |  |

| I <sub>OK</sub>  | DC output diode current                                    | $V_O > V_{DD}$ or $V_O < 0$                                                     | _    | ±50                   | mA   |  |

| Vo               | DC output voltage                                          | Note 2                                                                          | -0.5 | V <sub>DD</sub> + 0.5 | V    |  |

| Ιο               | DC output source or sink current                           | $V_O = 0$ to $V_{DD}$                                                           | _    | ±50                   | mA   |  |

| T <sub>stg</sub> | Storage temperature range                                  |                                                                                 | -65  | +150                  | °C   |  |

| P <sub>tot</sub> | Power dissipation per package plastic medium-shrink (SSOP) | For temperature range: -40 to +125°C above +55°C derate linearly with 11.3 mW/K | _    | 850                   | mW   |  |

#### NOTES:

### **DC OPERATING CONDITIONS**

| CVMDOL            | DADAMETED                                       | CONDITIONS               | LIM                   | ITS            | LINUT | NOTES |

|-------------------|-------------------------------------------------|--------------------------|-----------------------|----------------|-------|-------|

| SYMBOL            | PARAMETER                                       | CONDITIONS               | MIN                   | MAX            | UNIT  | NOTES |

| $V_{DD3}$         | DC 3.3 V supply voltage                         |                          | 3.135                 | 3.465          | V     |       |

| $AV_{DD}$         | DC 3.3 V analog supply voltage                  |                          | 3.135                 | 3.465          | V     |       |

| V <sub>IH</sub>   | 3.3 V HIGH-level input voltage                  |                          | 2.0                   | $V_{DD} + 0.3$ | V     |       |

| $V_{IL}$          | 3.3 V HIGH-level input voltage                  |                          | V <sub>SS</sub> - 0.3 | 0.8            | V     |       |

| V <sub>OL3</sub>  | 3.3 V LOW-level input voltage                   | I <sub>OL</sub> = 1.0 mA | _                     | 0.4            | V     |       |

| V <sub>OH3</sub>  | 3.3 V HIGH-level input voltage                  | I <sub>OH</sub> = 1.0 mA | 2.4                   | _              | V     |       |

| ILI               | Input leakage current                           | $0 < V_{IN} < V_{DD}$    | -5                    | +5             | μΑ    | 1     |

| f <sub>ref</sub>  | reference frequency, oscillator normal value    |                          | 14.31818              | 14.31818       | MHz   |       |

| C <sub>IN</sub>   | Input pin capacitance                           |                          | _                     | 5              | pF    | 2     |

| C <sub>XTAL</sub> | Xtal pin capacitance                            |                          | 13.5                  | 22.5           | pF    | 3     |

| C <sub>OUT</sub>  | Output pin capacitance                          |                          | _                     | 6              | pF    | 2     |

| L <sub>PIN</sub>  | Pin inductance                                  |                          |                       | 7              | nΗ    | 2     |

| T <sub>amb</sub>  | Operating ambient temperature range in free air |                          | 0                     | +70            | °C    |       |

#### NOTES:

- 1. Input leakage current does not include inputs with pull up or pull down resistors.

- 2. This is a recommendation, not an absolute requirement.

- 3. As seen by the crystal. Device is intended to be used with a 17-20 pF AT crystal.

<sup>1.</sup> Stresses beyond those listed may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>2.</sup> The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

## CK408 (66/100/133/200 MHz) spread spectrum differential system clock generator

PCK2023

### **POWER MANAGEMENT**

| CONDITION                    | MAXIMUM 3.3 V SUPPLY CONSUMPTION MAXIMUM DISCRETE CAP LOADS, $V_{DDL}$ = 3.465 V ALL STATIC INPUTS = $V_{DD3}$ OR $V_{SS}$ |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Power-down mode (PWRDWN = 0) | 25 mA @ $I_{ref}$ = 2.32 mA 46 mA @ $I_{ref}$ = 5.0 mA                                                                     |

| Full active                  | 280 mA                                                                                                                     |

### **CPU STOP FUNCTIONALITY**

| CPU_STOP | CPU                 | CPU    | 3V66   | 66BUFF   | PCIF/PCI   | USB/DOT |

|----------|---------------------|--------|--------|----------|------------|---------|

| 1        | Normal              | Normal | 66 MHz | 66 input | 66 input/2 | 48 MHz  |

| 0        | I <sub>ref</sub> *2 | Float  | 66 MHz | 66 input | 66 input/2 | 48 MHz  |

### DC CHARACTERISTICS

|                  |                                  |                       | TEST CONDITION                               | IC.                |     | LIMITS                         |      |      |

|------------------|----------------------------------|-----------------------|----------------------------------------------|--------------------|-----|--------------------------------|------|------|

| SYMBOL           | PARAMETER                        |                       | TEST CONDITIONS                              |                    |     | T <sub>amb</sub> = 0 to +70 °C |      |      |

|                  |                                  | V <sub>DD</sub> (V)   | ОТ                                           | HER                | MIN | TYP                            | MAX  | 1    |

|                  | 48 MHz USB, VCH                  | 3.135                 | V <sub>OUT</sub> = 1.0 V                     | Type 3A            | -29 | _                              | _    | mA   |

| Іон              | 46 WITZ USB, VCT                 | 3.465                 | V <sub>OUT</sub> = 3.135 V                   | 12-60 Ω            | _   | _                              | -23  | IIIA |

|                  | 48 MHz USB, VCH                  | 3.135                 | V <sub>OUT</sub> = 1.95 V                    | Type 3A            | 29  | _                              | _    | mA   |

| l <sub>OL</sub>  | 46 MINZ USB, VCN                 | 3.465                 | V <sub>OUT</sub> = 0.4 V                     | 12-60 Ω            | _   | _                              | 27   | MA   |

|                  | 40 MUz DOT                       | 3.135                 | V <sub>OUT</sub> = 1.0 V                     | Type 3B            | -29 | _                              | _    | mA   |

| Іон              | 48 MHz DOT                       | 3.465                 | V <sub>OUT</sub> = 3.135 V                   | 12-60 Ω            | _   | _                              | -23  | MA   |

|                  | 48 MHz DOT                       | 3.135                 | V <sub>OUT</sub> = 1.95 V                    | Type 3B            | 29  | _                              | _    | A    |

| l <sub>OL</sub>  | 46 MINZ DOT                      | 3.465                 | V <sub>OUT</sub> = 0.4 V                     | 12-60 Ω            | _   | _                              | 27   | mA   |

|                  | REF, PCI, PCIF,                  | 3.135                 | V <sub>OUT</sub> = 1.0 V                     | Type 5             | -33 | _                              | _    | mA   |

| Іон              | 3V66, 66BUFF                     | 3.465                 | V <sub>OUT</sub> = 3.135 V                   | 12-55 Ω            | _   | _                              | -33  | MA   |

|                  | REF, PCI, PCIF,                  | 3.135                 | V <sub>OUT</sub> = 1.95 V                    | Type 5             | 30  | _                              | _    | mA   |

| l <sub>OL</sub>  | 3V66, 66BUFF                     | 3.465                 | V <sub>OUT</sub> = 0.4 V                     | 12-55 Ω            | _   | _                              | 38   | MA   |

| V <sub>OL</sub>  | CPU/CPU                          | V <sub>SS</sub> = 0.0 | $R_S = 33.2 \Omega$<br>$R_P = 49.9 \Omega$   | Type X1            | 0.0 | _                              | 0.05 | ٧    |

| ±I <sub>I</sub>  | Input leakage current            | 3.365                 | 0 < V <sub>IN</sub> < V <sub>DD3</sub>       | _                  | -5  | _                              | 5    | μΑ   |

| ±l <sub>OZ</sub> | 3-State output OFF-State current | 3.465                 | V <sub>OUT</sub> =<br>V <sub>DD</sub> or GND | I <sub>O</sub> = 0 | _   | _                              | 10   | μА   |

7

NOTE:

<sup>1.</sup> All clock outputs loaded with maximum lump capacitance test load specified in AC characteristics section.

## CK408 (66/100/133/200 MHz) spread spectrum differential system clock generator

PCK2023

### **AC CHARACTERISTICS**

$V_{DD3} = 3.3 \text{ V } -5\%$ ;  $f_{crystal} = 14.31818 \text{ MHz}$

### **3V66 66 MHz TIMING REQUIREMENTS**

| SYMBOL              | PARAMETER                  |      | NITS<br>to +70 °C | UNIT | NOTES |

|---------------------|----------------------------|------|-------------------|------|-------|

|                     |                            | MIN  | MAX               |      |       |

| T <sub>PERIOD</sub> | period                     | 15.0 | 15.3              | ns   | 8, 13 |

| t <sub>HIGH</sub>   | HIGH time                  | 4.95 | N/A               | ns   | 9     |

| t <sub>LOW</sub>    | LOW time                   | 4.55 | N/A               | ns   | 10    |

| t <sub>RISE</sub>   | rise time                  | 0.5  | 2.0               | ns   | 12    |

| t <sub>FALL</sub>   | fall time                  | 0.5  | 2.0               | ns   | 12    |

| t <sub>JITTER</sub> | cycle-to-cycle jitter      | _    | 250               | ps   |       |

| Edge rate           | rising edge rate           | 1.0  | 4.0               | V/ns | 12    |

| Edge rate           | falling edge rate          | 1.0  | 4.0               | V/ns | 12    |

| t <sub>SKEW</sub>   | pin-to-pin skew 3V66 [1:0] | 0.0  | 250               | ps   |       |

| tskew               | pin-to-pin skew 3V66 [5:2] | 0.0  | 250               | ps   |       |

| t <sub>SKEW</sub>   | pin-to-pin skew 3V66 [5:0] | 0.0  | 450               | ps   |       |

### **66 MHz BUFFERED TIMING REQUIREMENTS**

| SYMBOL            | PARAMETER                                   |     | MITS<br>) to +70 °C | UNITS | NOTES |

|-------------------|---------------------------------------------|-----|---------------------|-------|-------|

|                   |                                             | MIN | MAX                 |       |       |

| t <sub>RISE</sub> | rise time                                   | 0.5 | 2.0                 | ns    | 12    |

| t <sub>FALL</sub> | fall time                                   | 0.5 | 2.0                 | ns    | 12    |

| t <sub>PD</sub>   | propagation delay from 66In to 66BUFF [2:0] | 2.5 | 4.5                 | ns    |       |

| Edge rate         | rising edge rate                            | 1.0 | 4.0                 | V/ns  | 12    |

| Edge rate         | falling edge rate                           | 1.0 | 4.0                 | V/ns  | 12    |

| t <sub>SKEW</sub> | 66 MHz buffered pin-to-pin skew             | 0.0 | 175                 | ps    |       |

### **PCIF/PCI AC TIMING REQUIREMENTS**

| SYMBOL              | PARAMETER                         |      | MITS<br>0 to +70 °C | UNITS | NOTES |

|---------------------|-----------------------------------|------|---------------------|-------|-------|

|                     |                                   | MIN  | MAX                 | 7     |       |

| T <sub>PERIOD</sub> | period                            | 30.0 | N/A                 | ns    | 8, 13 |

| t <sub>HIGH</sub>   | HIGH time                         | 12.0 | N/A                 | ns    | 9     |

| t <sub>LOW</sub>    | LOW time                          | 12.0 | N/A                 | ns    | 10    |

| t <sub>RISE</sub>   | RISE rise time                    |      | 2.0                 | ns    | 12    |

| t <sub>FALL</sub>   | fall time                         | 0.5  | 2.0                 | ns    | 12    |

| t <sub>JITTER</sub> | cycle-to-cycle jitter             | _    | _                   | ps    |       |

| Edge rate           | rising edge rate                  | 1.0  | 4.0                 | V/ns  | 12    |

| Edge rate           | Edge rate falling edge rate       |      | 4.0                 | V/ns  | 12    |

| t <sub>SKEW</sub>   | t <sub>SKEW</sub> pin-to-pin skew |      | 500                 | ps    |       |

| t <sub>PCI</sub>    | 3V66 [5:0] leads 33 MHz PCI       | 1.5  | 3.5                 | ns    |       |

8

## CK408 (66/100/133/200 MHz) spread spectrum differential system clock generator

PCK2023

### **USB 48 MHz AC TIMING REQUIREMENTS**

| SYMBOL                        | PARAMETER                                 | LIMI <sup>*</sup><br>T <sub>amb</sub> = 0 to |        | UNITS | NOTES |

|-------------------------------|-------------------------------------------|----------------------------------------------|--------|-------|-------|

|                               |                                           | MIN                                          | MAX    |       |       |

| T <sub>PERIOD</sub> (average) | period                                    | nominal =                                    | 20.829 | ns    |       |

| t <sub>HIGH</sub>             | HIGH time                                 | 8.094                                        | 10.036 | ns    |       |

| t <sub>LOW</sub>              | / LOW time                                |                                              | 9.836  | ns    |       |

| f                             | frequency                                 | 48.000                                       | 48.008 | MHz   | 8     |

| t <sub>RISE</sub>             | rise time                                 | 1.0                                          | 2.0    | ns    | 12    |

| t <sub>FALL</sub>             | fall time                                 | 1.0                                          | 2.0    | ns    | 12    |

| t <sub>JITTER</sub>           | t <sub>JITTER</sub> cycle-to-cycle jitter |                                              | 350    | ps    |       |

| Edge rate                     | Edge rate rising edge rate                |                                              | 2.0    | V/ns  |       |

| Edge rate                     | falling edge rate                         | 1.0                                          | 2.0    | V/ns  |       |

### **DOT 48 MHz AC TIMING REQUIREMENTS**

| SYMBOL                        | PARAMETER             | LIMI<br>T <sub>amb</sub> = 0 t |        | UNITS | NOTES |

|-------------------------------|-----------------------|--------------------------------|--------|-------|-------|

|                               |                       | MIN                            |        | 1     |       |

| T <sub>PERIOD</sub> (average) | period                | nominal =                      | ns     |       |       |

| t <sub>HIGH</sub>             | HIGH time             | 8.094                          | 10.036 | ns    |       |

| t <sub>LOW</sub>              | LOW time              | 7.694                          | 9.836  | ns    |       |

| f                             | frequency             | 48.000                         | 48.008 | MHz   | 8     |

| t <sub>RISE</sub>             | rise time             | 0.5                            | 1.0    | ns    | 12    |

| t <sub>FALL</sub>             | fall time             | 0.5                            | 1.0    | ns    | 12    |

| t <sub>JITTER</sub>           | cycle-to-cycle jitter | _                              | 350    | ps    |       |

| Edge rate                     | rising edge rate      | 2.0                            | 4.0    | V/ns  |       |

| Edge rate falling edge rate   |                       | 2.0                            | 4.0    | V/ns  |       |

| t <sub>SKEW</sub> USB to DOT  |                       | _                              | 1000   | ps    |       |

## CK408 (66/100/133/200 MHz) spread spectrum differential system clock generator

PCK2023

### **CPU 0.7 V AC TIMING REQUIREMENTS**

| OVMDOL                       | DADAMETED                                                              | CPU 2 | 00 MHz | CPU 1 | 33 MHz | CPU 10 | 00 MHz | CPU 6 | 66 MHz |       | NOTEO    |

|------------------------------|------------------------------------------------------------------------|-------|--------|-------|--------|--------|--------|-------|--------|-------|----------|

| SYMBOL                       | PARAMETER                                                              | MIN   | MAX    | MIN   | MAX    | MIN    | MAX    | MIN   | MAX    | UNITS | NOTES    |

| T <sub>PERIOD</sub>          | average period                                                         | 5.0   | 5.1    | 7.5   | 7.65   | 10.0   | 10.2   | 15.0  | 15.3   | ns    | 1, 7     |

| t <sub>ABSMIN</sub>          | absolute<br>minimum host<br>clock period                               | 4.8   | _      | 7.3   | _      | 9.8    | _      | 14.8  | _      | ns    | 1, 7     |

| t <sub>RISE</sub>            | rise time                                                              | 175   | 600    | 175   | 600    | 175    | 600    | 175   | 600    | ps    | 2, 7, 14 |

| t <sub>FALL</sub>            | fall time                                                              | 175   | 600    | 175   | 600    | 175    | 600    | 175   | 600    | ps    | 2, 7, 14 |

| $\Delta t_{RISE}$            | rise time<br>variation                                                 | _     | 150    | _     | 150    | _      | 150    | _     | 150    | ps    | 2, 7     |

| $\Delta t_{FALL}$            | fall time<br>variation                                                 | _     | 150    | _     | 150    | _      | 150    | _     | 150    | ps    | 2, 7     |

| V <sub>CROSS</sub>           | absolute<br>crossing point<br>voltages                                 | 280   | 430    | 280   | 430    | 280    | 430    | 280   | 430    | mV    | 7        |

| $\Delta V_{	ext{CROSS}}$     | total variation<br>of V <sub>CROSS</sub> for<br>rising edge of<br>host | _     | 90     | _     | 90     | _      | 90     | _     | 90     | mV    | 3, 7     |

| Total<br>ΔV <sub>CROSS</sub> | total variation<br>of V <sub>CROSS</sub><br>over all edges             | _     | 110    | _     | 110    | _      | 110    | _     | 110    | mV    | 4, 7     |

| <sup>t</sup> CCJITTER        | cycle-to-cycle<br>jitter                                               | _     | 150    | _     | 150    | _      | 150    | _     | 150    | ps    | 7, 15    |

| Duty Cycle                   |                                                                        | 45    | 55     | 45    | 55     | 45     | 55     | 45    | 55     | %     | 7        |

| Overshoot                    | maximum<br>voltage<br>allowed at<br>output                             | _     | 850    | _     | 850    | _      | 850    | -     | 850    | mV    | 7        |

| Undershoot                   | minimum<br>voltage<br>allowed at<br>output                             | _     | -150   | _     | -150   | _      | -150   | _     | -150   | mV    | 7        |

| tskew                        | pin-to-pin                                                             |       | 150    | _     | 150    | _      | 150    | _     | 150    | ps    |          |

## CK408 (66/100/133/200 MHz) spread spectrum differential system clock generator

PCK2023

### **CPU 1.0 V AC TIMING REQUIREMENTS**

| SYMBOL                          | DADAMETED                                                     | CPU 2 | 00 MHz | CPU 1 | 33 MHz | CPU 10 | 00 MHz | CPU 6 | 66 MHz | LINUTO | NOTES  |

|---------------------------------|---------------------------------------------------------------|-------|--------|-------|--------|--------|--------|-------|--------|--------|--------|

| STINIBUL                        | PARAMETER                                                     | MIN   | MAX    | MIN   | MAX    | MIN    | MAX    | MIN   | MAX    | UNITS  | NOTES  |

| T <sub>PERIOD</sub>             | average period                                                | 5.0   | 5.1    | 7.5   | 7.65   | 10.0   | 10.2   | 15.0  | 15.3   | ns     | 1, 15  |

| t <sub>ABSMIN</sub>             | absolute<br>minimum host<br>clock period                      | 4.85  | _      | 7.35  | _      | 9.85   | _      | 14.85 | _      | ns     | 1, 15  |

| Diff-t <sub>RISE</sub>          | rise time                                                     | 175   | 467    | 175   | 467    | 300    | 467    | 300   | 467    | ps     | 15, 16 |

| Diff-t <sub>FALL</sub>          | fall time                                                     | 175   | 467    | 175   | 467    | 175    | 467    | 175   | 467    | ps     | 15, 16 |

| SE Δ <sub>SKEW</sub>            | Absolute<br>single-ended<br>rise/fall<br>waveform<br>symmetry | -     | 325    | _     | 325    | _      | 325    | _     | 325    | ps     | 17, 18 |

| V <sub>CROSS</sub>              | absolute<br>crossing point<br>voltages                        | 0.51  | 0.76   | 0.51  | 76     | 0.51   | 76     | _     | _      | ٧      | 18     |

| tCCJITTER                       | cycle-to-cycle<br>jitter                                      | _     | 150    | _     | 150    | _      | 150    | _     | 150    | ps     | 15, 19 |

| Duty Cycle                      | _                                                             | 45    | 55     | 45    | 55     | 45     | 55     | 45    | 55     | %      | 15     |

| SE-V <sub>OH</sub>              | maximum<br>voltage<br>allowed at<br>output                    | .92   | 1.45   | .92   | 1.45   | .92    | 1.45   | .92   | 1.45   | V      | 18     |

| SE-V <sub>OL</sub>              | minimum<br>voltage<br>allowed at<br>output                    | -200  | 350    | -200  | 350    | -200   | 350    | -200  | 350    | mV     | 18     |

| Diff-<br>V <sub>RING_RISE</sub> | rising edge<br>ringback                                       | 0.35  | _      | 0.35  | _      | 0.35   | _      | 0.35  | _      | V      | 15     |

| Diff-<br>V <sub>RING_FALL</sub> | falling edge<br>ringback                                      | _     | -0.35  | _     | -0.35  | _      | -0.35  | _     | -0.35  | V      | 15     |

11

## CK408 (66/100/133/200 MHz) spread spectrum differential system clock generator

PCK2023

#### **ALL OUTPUTS**

| SYMBOL                             | PARAMETER                             | LIMIT:<br>T <sub>amb</sub> = 0 to |      | UNITS | NOTES |  |

|------------------------------------|---------------------------------------|-----------------------------------|------|-------|-------|--|

|                                    |                                       | MIN                               | MAX  |       |       |  |

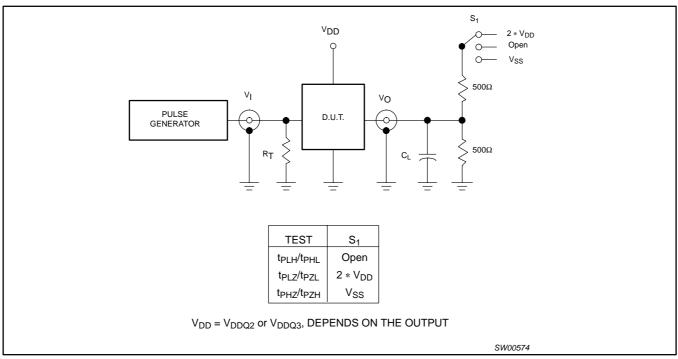

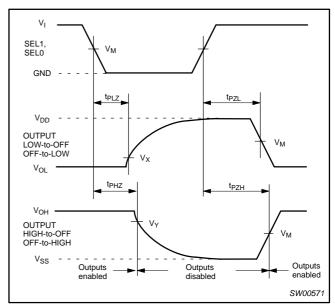

| t <sub>PZL</sub> /t <sub>PZH</sub> | output enable delay (all outputs)     | 1.0                               | 10.0 | ns    |       |  |

| t <sub>PZL</sub> /t <sub>PZH</sub> | output disable delay (all outputs)    | 1.0                               | 10.0 | ns    |       |  |

| t <sub>STABLE</sub>                | all clock stabilization from power-up | _                                 | 3    | ms    | 11    |  |

#### NOTES:

- 1. Measured at crossing points or where subtraction of CLK-CLK crosses 0 V.

- 2. Measured from  $V_{OL} = 0.175 \text{ V}$  to  $V_{OH} = 0.525 \text{ V}$ .

- 3. These crossing points refer to only crossing points containing a rising edge of a CPU output (as opposed to a CPU output).

- 4. This measurement refers to the total variation from the lowest crossing point to the highest, regardless of which edge is crossing.

- 5. Measured from  $V_{OI} = 0.2 \text{ V}$  to  $V_{OH} = 0.8 \text{ V}$ .

- 6. Determined as a fraction of 2\* (t<sub>RISE</sub>-t<sub>FALL</sub>)/(t<sub>RISE</sub>+t<sub>FALL</sub>).

- 7. Test load is  $R_S = 33.2 \Omega$ ,  $R_P = 49.9 \Omega$ .

- 8. Period, jitter, offset and skew measured at rising edge @ 1.5 V for 3.3 V clocks.

- 9. T<sub>HIGH</sub> is measured at 2.4 V for non-CPU outputs.

- 10. T<sub>LOW</sub> is measured at 0.4 V for all outputs.

- 11. The time specified is measured from when  $V_{DDQ}$  achieves its normal operating level (typical condition  $V_{DDQ} = 3.3 \text{ V}$ ) until the frequency output is stable and operating within specification.

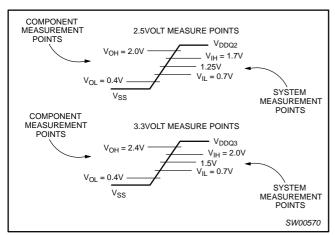

- 12. The 3.3 V clock t<sub>RISE</sub> and t<sub>FALL</sub> are measured as a transition through the threshold region V<sub>OL</sub> = 0.4 V and V<sub>OH</sub> = 2.4 V (1 mA) JEDEC specification.

- 13. The average period over any 1 µs period of time must be greater than the minimum specified period.

- 14. Designed for 150-420 ps (1 V/ns minimum rise time across 0.42 V).

- 15. Measurement taken from differential waveform.

- 16. Measurement taken from differential waveform from -0.35 to +0.35 V.

- 17. Measurements taken from common mode waveforms, measure rise/fall time from 0.41 to 0.86 V. Rise/fall time matching is defined as "the instantaneous difference between maximum CLK rise (fall) and minimum CLK fall (rise) time, or minimum CLK rise (fall) and maximum CLK fall (rise) time". This parameter is designed for waveform symmetry.

- 18. Measured in absolute voltage, single ended.

- 19. Cycle-to-cycle jitter measurements taken with minimum capacitive loading on non-CPU outputs.

## CK408 (66/100/133/200 MHz) spread spectrum differential system clock generator

PCK2023

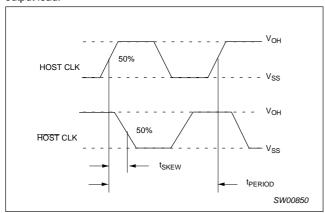

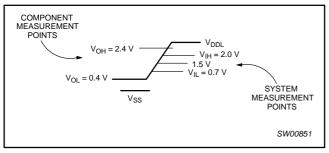

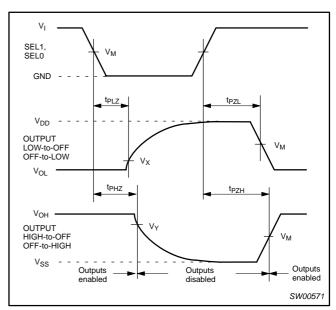

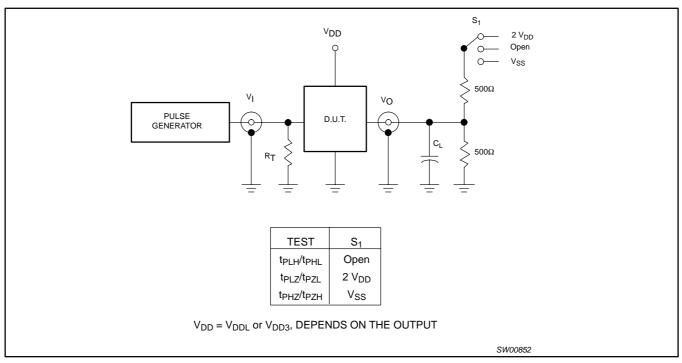

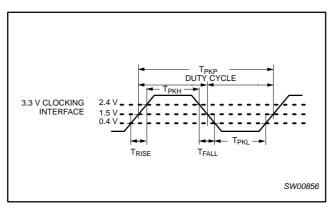

### **AC WAVEFORMS**

$\begin{array}{l} V_{M}=1.25~V~@~V_{DDL}~and~1.5~V~@~V_{DD3} \\ V_{X}=V_{OL}+0.3~V~\\ V_{Y}=V_{OH}-0.3~V~\\ V_{OL}~and~V_{OH}~are~the~typical~output~voltage~drop~that~occur~with~the~output~load. \end{array}$

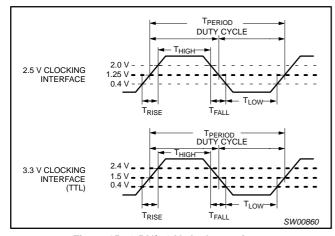

Figure 1. Host clock

Figure 2. 3.3 V clock waveforms

Figure 3. State enable and disable times

2003 Jul 31

13

## CK408 (66/100/133/200 MHz) spread spectrum differential system clock generator

PCK2023

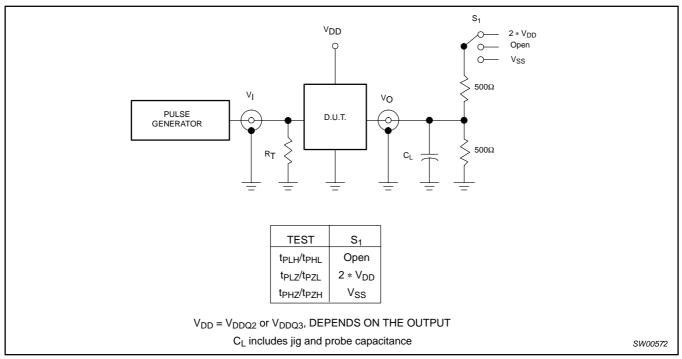

Figure 4. Load circuitry for switching times

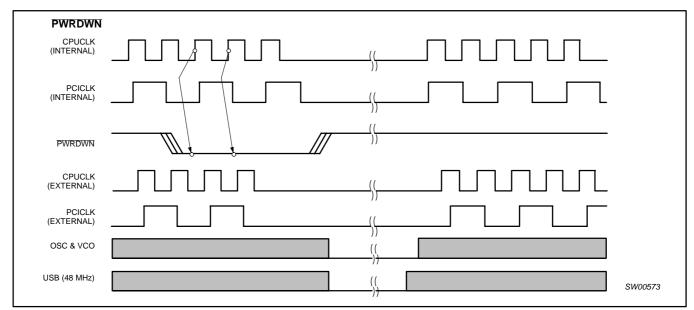

Figure 5. Power management

2003 Jul 31 14

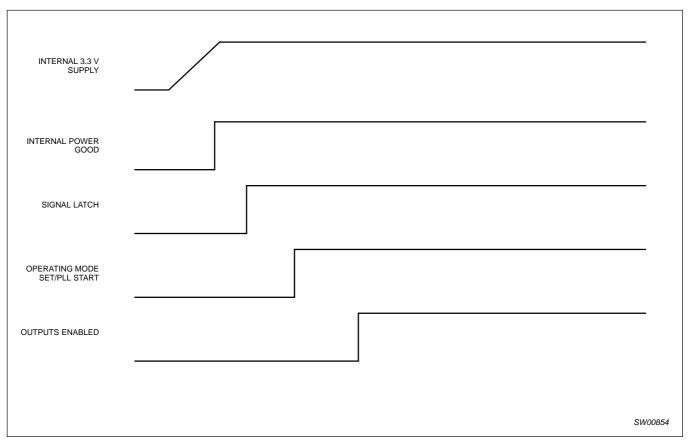

### **POWER-UP SEQUENCE**

Figure 6 shows the power-up sequence for the PCK2023. Once power is applied to the device, an internal sense circuit generates a signal when the supply is above approximately 2 volts. This signal generates a series of timed signals that control the sequential event inside the device. First, the multifunction pins are latched into the device. These latched signals are then used to define the mode of operation of the device. A short time later, the PLL is enabled and begins running. After XX ms, the clock outputs are enabled and begin running

Figure 6. Power-up sequence

Figure 7. Host clock measurements

15

## CK408 (66/100/133/200 MHz) spread spectrum differential system clock generator

PCK2023

Figure 8. 3.3 V clock waveforms

PCK2023

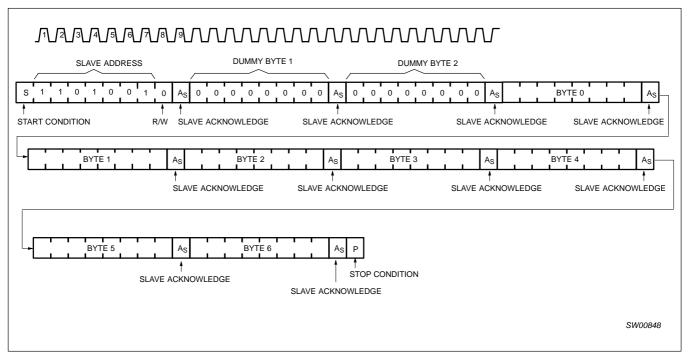

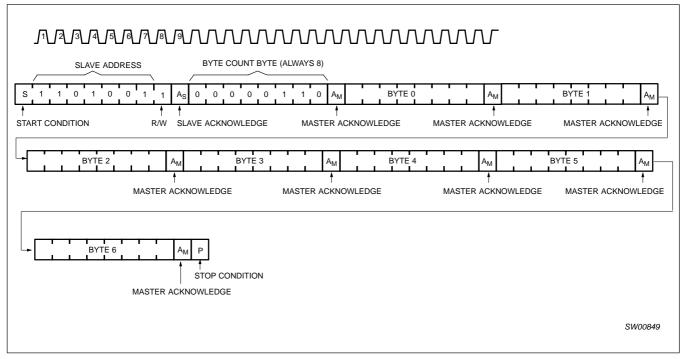

### I<sup>2</sup>C SPECIFICATION

Figure 9. I<sup>2</sup>C write

Figure 10. I<sup>2</sup>C read

17

# CK408 (66/100/133/200 MHz) spread spectrum differential system clock generator

PCK2023

### BYTE 0

| BIT | DESCRIPTION/FUNCTION                                                                                       | TYPE | POWER UP<br>CONDITION | OUTPUT(S)<br>AFFECTED                            | PIN AFFECTED                                      | SOURCE PIN |

|-----|------------------------------------------------------------------------------------------------------------|------|-----------------------|--------------------------------------------------|---------------------------------------------------|------------|

| 0   | S0 reflects the value of the Sel_0 pin sampled on power-up                                                 | R    | externally selected   | N/A                                              | N/A                                               | 54         |

| 1   | S1 reflects the value of the Sel_1 pin sampled on power-up                                                 | R    | externally selected   | N/A                                              | N/A                                               | 55         |

| 2   | S2 reflects the value of the Sel_2 pin sampled on power-up                                                 | R    | externally selected   | N/A                                              | N/A                                               | 40         |

| 3   | PCI_stop. This bit is ANDed with the PCI_STOP pin for I <sup>2</sup> C readback and control of PCI outputs | RW   | externally selected   | All PCI clock<br>outputs except<br>PCI[2:0] pins | 10, 11, 12, 13, 16,<br>17, 18                     | 34         |

| 4   | CPU_stop reflects the current value of the external CPU_Stop pin                                           | R    | externally selected   | All CPU clock pairs                              | 44, 45, 48, 49, 51,<br>52                         | 53         |

| 5   | VCH select 66 MHz/48MHz<br>enabled                                                                         | RW   | 0 = 66MHz enabled     | 3V66_1/VCH                                       | 35                                                | N/A        |

| 6   | not used                                                                                                   | _    | 0                     | _                                                | _                                                 | _          |

| 7   | spread spectrum enabled                                                                                    | RW   | 0 = spread off        | CPU[2:0],<br>3V66[1:0]                           | 5, 6, 7, 10, 11, 12,<br>13, 16, 17, 18, 33,<br>35 | N/A        |

### BYTE 1

| BIT | DESCRIPTION/FUNCTION                                                               | TYPE | POWER UP<br>CONDITION                               | OUTPUT(S)<br>AFFECTED | PIN AFFECTED | SOURCE PIN |

|-----|------------------------------------------------------------------------------------|------|-----------------------------------------------------|-----------------------|--------------|------------|

| 0   | CPU0 output enable<br>1 = enabled<br>0 = disabled                                  | RW   | 1 = enabled                                         | CPU0<br>CPU0          | 51, 52       | N/A        |

| 1   | CPU1 output enable<br>1 = enabled<br>0 = disabled                                  | RW   | 1 = enabled                                         | CPU1<br>CPU1          | 48, 49       | 55         |

| 2   | CPU2 output enable<br>1 = enabled<br>0 = disabled                                  | RW   | 1 = enabled                                         | CPU2<br>CPU2          | 44, 45       | 40         |

| 3   | allow control of CPU0 with<br>assertion of CPU_Stop<br>1 = enabled<br>0 = disabled | RW   | 0 = not free running,<br>is affected by<br>CPU_Stop | CPU0<br>CPU0          | 51, 52       | 34         |

| 4   | allow control of CPU1 with<br>assertion of CPU_Stop<br>1 = enabled<br>0 = disabled | RW   | 0 = not free running,<br>is affected by<br>CPU_Stop | CPU1<br>CPU1          | 48, 49       | 53         |

| 5   | allow control of CPU2 with<br>assertion of CPU stop<br>1 = enabled<br>0 = disabled | RW   | 0 = not free running,<br>is affected by<br>CPU_Stop | CPU2<br>CPU2          | 44, 45       | N/A        |

| 6   | not used                                                                           |      | 0                                                   | _                     | _            | _          |

| 7   | CPU Mult0 value sampled at startup                                                 | R    | externally selected                                 | N/A                   | N/A          | 43         |

18

# CK408 (66/100/133/200 MHz) spread spectrum differential system clock generator

PCK2023

### BYTE 2

| BIT | DESCRIPTION/FUNCTION                               | TYPE | POWER UP<br>CONDITION | OUTPUT(S)<br>AFFECTED | PIN AFFECTED | SOURCE PIN |

|-----|----------------------------------------------------|------|-----------------------|-----------------------|--------------|------------|

| 0   | PCI0 output enabled<br>1 = enabled<br>0 = disabled | RW   | 1 = enabled           | PCI0                  | 10           | N/A        |

| 1   | PCI1 output enabled<br>1 = enabled<br>0 = disabled | RW   | 1 = enabled           | PCI1                  | 11           | N/A        |

| 2   | PCI2 output enabled<br>1 = enabled<br>0 = disabled | RW   | 1 = enabled           | PCI2                  | 12           | N/A        |

| 3   | PCI3 output enabled<br>1 = enabled<br>0 = disabled | RW   | 1 = enabled           | PCI3                  | 13           | N/A        |

| 4   | PCI4 output enabled<br>1 = enabled<br>0 = disabled | RW   | 1 = enabled           | PCI4                  | 16           | N/A        |

| 5   | PCI5 output enabled<br>1 = enabled<br>0 = disabled | RW   | 1 = enabled           | PCI5                  | 17           | N/A        |

| 6   | PCI6 output enabled<br>1 = enabled<br>0 = disabled | RW   | 1 = enabled           | PCI6                  | 18           | N/A        |

| 7   | not used                                           |      | 0                     | N/A                   | N/A          | N/A        |

### BYTE 3

| ВІТ | DESCRIPTION/FUNCTION                                                                         | TYPE | POWER UP<br>CONDITION                           | OUTPUT(S)<br>AFFECTED | PIN AFFECTED | SOURCE PIN |

|-----|----------------------------------------------------------------------------------------------|------|-------------------------------------------------|-----------------------|--------------|------------|

| 0   | PCIF0 output enabled                                                                         | RW   | 1 = enabled                                     | PCIF0                 | 5            | N/A        |

| 1   | PCIF1 output enabled                                                                         | RW   | 1 = enabled                                     | PCIF1                 | 6            | N/A        |

| 2   | PCIF2 output enabled                                                                         | RW   | 1 = enabled                                     | PCIF2                 | 7            | N/A        |

| 3   | allow control of PCIF0 with assertion of PCI_Stop 0 = free running 1 = stopped with PCI_Stop | RW   | 0 = free running not<br>affected by<br>PCI_Stop | PCIF0                 | 5            | N/A        |

| 4   | allow control of PCIF1 with assertion of PCI_Stop 0 = free running 1 = stopped with PCI_Stop | RW   | 0 = free running not<br>affected by<br>PCI_Stop | PCIF1                 | 6            | N/A        |

| 5   | allow control of PCIF2 with assertion of PCI_Stop 0 = free running 1 = stopped with PCI_Stop | RW   | 0 = free running not<br>affected by<br>PCI_Stop | PCIF2                 | 7            | N/A        |

| 6   | USB 48MHz output enabled                                                                     | RW   | 1 = enabled                                     | USB 48MHz             | 39           | N/A        |

| 7   | DOT 48 MHz output<br>enabled                                                                 | RW   | 1 = enabled                                     | DOT 48MHz             | 38           | N/A        |

19

# CK408 (66/100/133/200 MHz) spread spectrum differential system clock generator

PCK2023

BYTE 4

| BIT | DESCRIPTION/FUNCTION                                        | TYPE | POWER UP CONDITION | OUTPUT(S) AFFECTED | PIN NUMBER |

|-----|-------------------------------------------------------------|------|--------------------|--------------------|------------|

| 0   | 66Buff0/3V66_2 output enabled 1 = enabled 0 = disabled      | RW   | 1 = enabled        | 66Buff0/3V66_2     | 21         |

| 1   | 66Buff1/3V66_3 output enabled 1 = enabled 0 = disabled      | RW   | 1 = enabled        | 66Buff1/3V66_3     | 22         |

| 2   | 66Buff2/3V66_4 output enabled 1 = enabled 0 = disabled      | RW   | 1 = enabled        | 66Buff2/3V66_4     | 23         |

| 3   | 3V66_5 output enabled<br>1 = enabled<br>0 = disabled        | RW   | 1 = enabled        | 3V66_5             | 24         |

| 4   | 3V66_1/VCH output<br>enabled<br>1 = enabled<br>0 = disabled | RW   | 1 = enabled        | 3V66_1/VCH         | 35         |

| 5   | 3V66_0 output enabled<br>1 = enabled<br>0 = disabled        | RW   | 1 = enabled        | 3V66_0             | 33         |

| 6   | not used                                                    | _    | 0                  | _                  | _          |

| 7   | not used                                                    | _    | 0                  | _                  | _          |

### BYTE 5

| BIT | DESCRIPTION/FUNCTION  | TYPE | POWER UP CONDITION | OUTPUT(S) AFFECTED | PIN NUMBER |

|-----|-----------------------|------|--------------------|--------------------|------------|

| 0   | USB edge rate control | RW   | 0                  | USB                | 39         |

| 1   | OOD eage rate control | RW   | 0                  | USB                | 39         |

| 2   | DOT edge rate control | RW   | 0                  | DOT                | 38         |

| 3   | DOT edge rate control | RW   | 0                  | DOT                | 38         |

| 4   | not used              | _    | 0                  | _                  | _          |

| 5   | not used              | _    | 0                  | _                  | _          |

| 6   | not used              | _    | 0                  | _                  | _          |

| 7   | not used              |      | 0                  | _                  | _          |

### BYTE 6

| BIT | DESCRIPTION/FUNCTION | TYPE | POWER UP CONDITION | OUTPUT(S) AFFECTED | PIN NUMBER |

|-----|----------------------|------|--------------------|--------------------|------------|

| 0   | vendor ID bit 0      | R    | 1                  | N/A                | N/A        |

| 1   | vendor ID bit 1      | R    | 1                  | N/A                | N/A        |

| 2   | vendor ID bit 2      | R    | 1                  | N/A                | N/A        |

| 3   | vendor ID bit 3      | R    | 0                  | N/A                | N/A        |

| 4   | revision code bit 0  | R    | 0                  | N/A                | N/A        |

| 5   | revision code bit 1  | R    | 0                  | N/A                | N/A        |

| 6   | revision code bit 2  | R    | 0                  | N/A                | N/A        |

| 7   | revision code bit 3  | R    | 0                  | N/A                | N/A        |

## CK408 (66/100/133/200 MHz) spread spectrum differential system clock generator

PCK2023

#### **APPLICATION NOTES**

Optimum performance of the PCK2023 can only be achieved through correct implementation in the system board. This application note addresses many of the issues associated with integrating the PCK2023 on a system board. Descriptions for circuit board layout and decoupling are provided in this application note.

### Circuit board layout

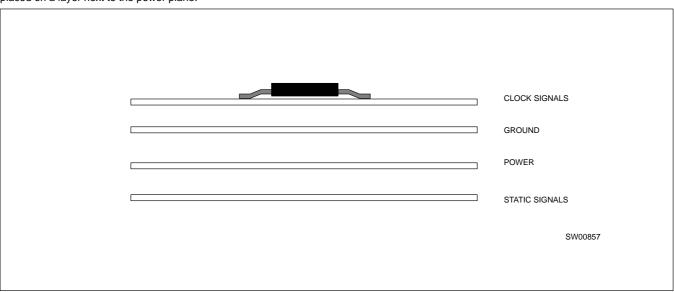

It is possible to generate a circuit board with the proper characteristics using four-layer configuration. Figure 11 shows the layer stack-up. It is critical to keep the clock signals on a plane next to a ground plane to ensure they are ground referenced otherwise the clock signals may experience significant distortion and added jitter. Static signals (such as SPREAD, PWRDWN, etc.) can be placed on a layer next to the power plane.

The components associated with the clocks should be placed on the same layer as the PCK2023 IC. This will allow the layout to avoid the use of vias for interconnect, thereby reducing node capacitance and trace inductance. All components should be placed as close to the IC as possible.

Figure 11. Optimum board layout

2003 Jul 31 21

## CK408 (66/100/133/200 MHz) spread spectrum differential system clock generator

PCK2023

### Component decoupling

Decoupling is another important consideration to ensure optimum operation of the PCK2023. A first pass decoupling capacitor value may be determined by applying the following equation:

$$C_{bypass} = \frac{1}{2pF_{psw}X_{max}}$$

where

$$X_{max} = \frac{\Delta V}{\Delta I}$$

$$F_{psw} = \frac{X_{max}}{2pL_{psw}}$$

$\Delta V$  is the maximum supply noise permitted (20 mV, for example)

ΔI is the maximum current draw for the clock

L<sub>psw</sub> is the power supply lead inductance

$\ensuremath{\mathsf{F}_{\mathsf{pSW}}}$  is the frequency below which the power supply wiring is adequate

The maximum current may be determined by considering the switching of the clock outputs and the capacitive load on these outputs. The following equation may be used to determine the current per output. Once the current for each clock output is determined, they can be summed to determine the total switching current.

$$i = C_{load} \frac{dV}{dt}$$

Most of these values can be determined from the usage in the board design. For example, the IOCLK has a specified edge rate of 1.25 ns typical when slewing between 0.7 and 2.4 volts and the maximum  $C_{load}$  is 30 pF. The HOST outputs are a special case since, although the output either drives current or is off, only one drives at a time, so the current is really steered rather than switched. The act of steering the current reduces switching noise on these supplies, therefore the HOST supplies require less decoupling. As a starting point, assume the supply current for each HOST output is equal to 1/2 the programmed output current.

Decoupling capacitors should be located as close to the power pins on the IC as possible. The use of too much decoupling should be avoided since it could cause oscillations on the part because of the LC circuit (the IC leads act as inductors). Also, it is possible to cause oscillations from resonance between the board inductance and board capacitance. Two capacitors may be placed in parallel to effectively extend the capacitance range of the decoupling since the larger capacitor will have a self-resonance at a lower frequency than the smaller capacitor. When using this method, the split between values should be 100 (i.e., 0.1  $\mu F$  and 0.001  $\mu F$ ).

Another consideration when selecting the decoupling capacitors is the dielectric material of the capacitor. This will depend on the frequency range of concern. For lower frequencies, Z5U material may be used since this type of capacitor has a self-resonance in the 1 MHz to 20 MHz range. Capacitors of NPO have a self-resonance much higher and are more for high frequency decoupling. Consult a

capacitor manufacture's datasheet to determine the optimum material type to use.

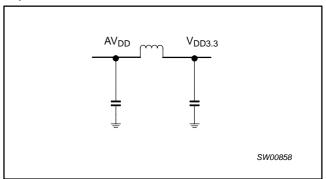

Additional filtering on the Analog supplies (AVDD) may be used to reduce the noise coupled from the circuit board global VDD to the internal V<sub>DD</sub> of the PCK2023. One way to do this is to use a PI filter. The specific values should be selected to allow proper decoupling on the pin side while rejecting the digital switching noise. A spectrum analyzer can provide considerable insight to ensure optimum values are selected. Measure the frequency content of the supply on either side of the inductor to verify the values selected reduce the noise on the component side of the filter. To provide the maximum isolation, each AV<sub>DD</sub> line should have a separate filter since the internal circuitry using these lines have very different switching requirements. In general, pin 26 is strictly a static current draw and should not have any switching noise. Great care has been taken to reduce the sensitivity to supply noise, but there is a finite limit to the capability to do this, therefore added filtering on the board should enhance performance. Pin 46 is used as a supply to the internal PLLs. This node will contain some high frequency switching noise since the internal PLLs operate up to 200 MHz. Again, additional filtering will improve the performance of the part. If a single filter is used for both supplies, noise from the PLL supply (pin 46) can couple int the  $I_{ref}$  supply (pin 42) and increase the jitter of the HOST outputs.

Figure 12. PI filter for all analog  $V_{\mbox{\scriptsize DD}}$  lines

### I<sub>ref</sub> decoupling

22

Filtering on the  $I_{ref}$  supply has already been discussed, but additional filtering can be added on the  $I_{ref}$  pin (pin 42) to perform additional filtering of the reference current. This reference current is critical to the performance of the HOST outputs since variation in this current is directly proportional to jitter on the HOST outputs. On-die decoupling has been included to reduce noise on this node, but additional decoupling could also be used to further reduce any noise. Care must be taken with this approach to ensure the capacitor and reference resistor share the same ground. Placing both components side by side is an optimum configuration. This external capacitor should not exceed TBD pF to ensure the current source inside the PCK2023 can supply enough charge for this node to reach reference value (1.1 volt).

## CK408 (66/100/133/200 MHz) spread spectrum differential system clock generator

PCK2023

#### **Functional connection**

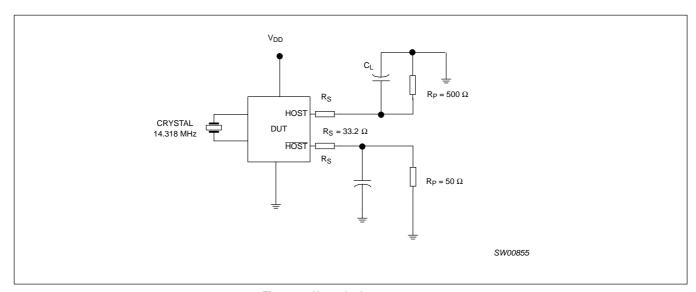

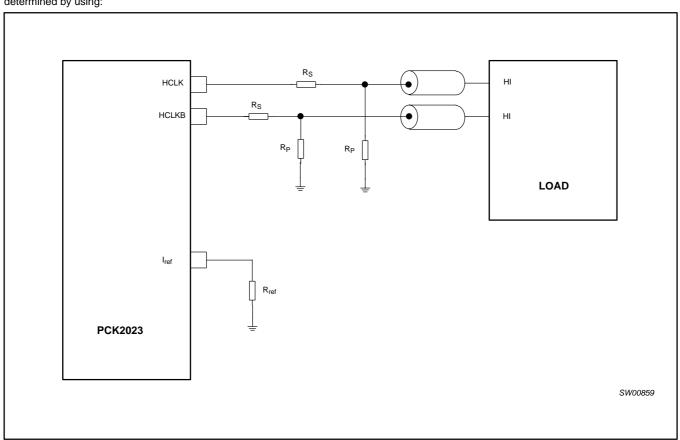

Figure 13 shows a partial diagram of the PCK2023 in an application. The host outputs are differential current drivers, therefore the output current is converted to a voltage by using some type of load resistor (in this case,  $R_{\rm S}$  and  $R_{\rm P}$ ). The output current is based on two, the value of  $R_{\rm ref}$  and the setting on MULTSEL0 and MULTSEL1 pins. The  $I_{\rm ref}$  pin is actually a reference voltage which is fixed at 1.1 volts, therefore,  $I_{\rm ref}$  is 1.1/ $R_{\rm ref}$ . There are limitations on how large the current can be made. This is coupled to the termination resistors used. The maximum voltage which should be observed at the HOST or  $\overline{\rm HOST}$  pins of the PCK2023 is 1.1 volts. This value may be determined by using:

$$V_{\text{max}} = (R_s + R_P) N_{\text{mult}} \frac{1.1}{R_{\text{ref}}}$$

where  $R_S$  and  $R_P$  are the termination resistor values,  $N_{mult}$  is the current multiplier set by MULTSEL0 and MULTSEL1, and  $R_{ref}$  is the current reference resistor.  $V_{max}$  should not exceed 1.1 volts because of the internal current source configuration.

Figure 13. PCK2023 implementation in a circuit board

2003 Jul 31 23

## CK408 (66/100/133/200 MHz) spread spectrum differential system clock generator

PCK2023

Figure 14. Host clock measurements

24

Figure 15. 2.5 V/3.3 V clock waveforms

## CK408 (66/100/133/200 MHz) spread spectrum differential system clock generator

PCK2023

### **AC WAVEFORMS**

$V_M = 1.25 \text{ V} @ V_{DDL} \text{ and } 1.5 \text{ V} @ V_{DD3}$  $V_{X} = V_{OL} + 0.3 \text{ V}$   $V_{Y} = V_{OH} - 0.3 \text{ V}$   $V_{OL}$  and  $V_{OH}$  are the typical output voltage drop that occur with the

output load.

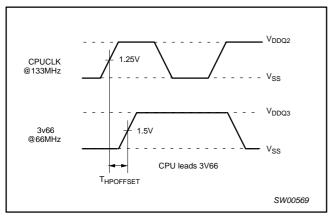

Figure 16. Host clock

Figure 17. 3.3 V clock waveforms

Figure 18. State enable and disable times

## CK408 (66/100/133/200 MHz) spread spectrum differential system clock generator

PCK2023

Figure 19. Load circuitry for switching times

Figure 20. Power management

26

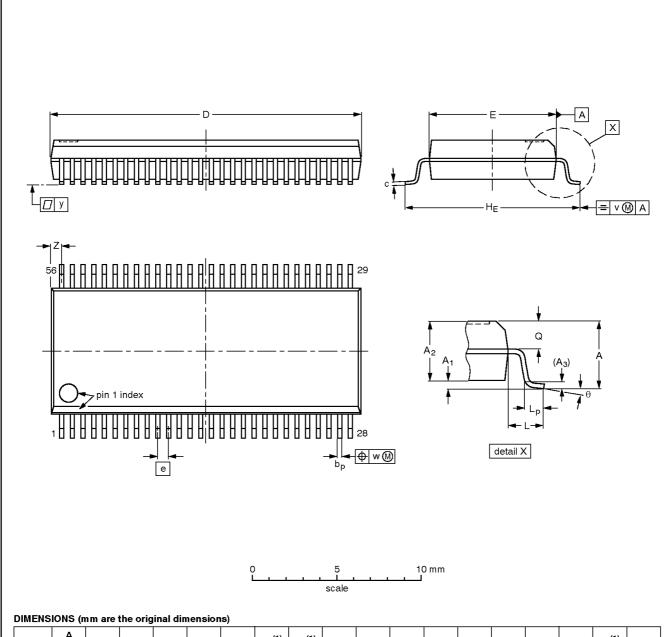

### plastic shrink small outline package; 56 leads; body width 7.5 mm

SOT371-1

| UNIT | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | A <sub>3</sub> | bp         | C            | D <sup>(1)</sup> | E <sup>(1)</sup> | е     | HE           | L   | Lp         | Q          | v    | w    | у   | Z <sup>(1)</sup> | θ        |

|------|-----------|----------------|----------------|----------------|------------|--------------|------------------|------------------|-------|--------------|-----|------------|------------|------|------|-----|------------------|----------|

| mm   | 2.8       | 0.4<br>0.2     | 2.35<br>2.20   | 0.25           | 0.3<br>0.2 | 0.22<br>0.13 | 18.55<br>18.30   | 7.6<br>7.4       | 0.635 | 10.4<br>10.1 | 1.4 | 1.0<br>0.6 | 1.2<br>1.0 | 0.25 | 0.18 | 0.1 | 0.85<br>0.40     | 8°<br>0° |

#### Note

1. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

| OUTLINE  |     | REFER  | RENCES | EUROPEAN   | ISSUE DATE                      |  |

|----------|-----|--------|--------|------------|---------------------------------|--|

| VERSION  | IEC | JEDEC  | EIAJ   | PROJECTION | ISSUEDATE                       |  |

| SOT371-1 |     | MO-118 |        |            | <del>95-02-04</del><br>99-12-27 |  |

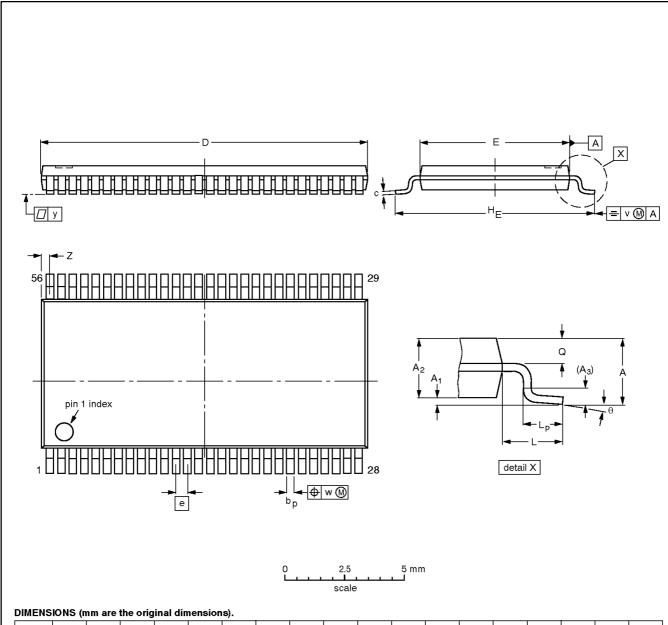

TSSOP56: plastic thin shrink small outline package; 56 leads; body width 6.1 mm

SOT364-1

| UNIT | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | А3   | bp           | С          | D <sup>(1)</sup> | E <sup>(2)</sup> | е   | HE         | L   | Lp         | Q            | ٧    | w    | у   | z          | θ        |

|------|-----------|----------------|----------------|------|--------------|------------|------------------|------------------|-----|------------|-----|------------|--------------|------|------|-----|------------|----------|

| mm   | 1.2       | 0.15<br>0.05   | 1.05<br>0.85   | 0.25 | 0.28<br>0.17 | 0.2<br>0.1 | 14.1<br>13.9     | 6.2<br>6.0       | 0.5 | 8.3<br>7.9 | 1.0 | 0.8<br>0.4 | 0.50<br>0.35 | 0.25 | 0.08 | 0.1 | 0.5<br>0.1 | 8°<br>0° |

#### Notes

2003 Jul 31

- 1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

- 2. Plastic interlead protrusions of 0.25 mm maximum per side are not included.

|     |        | EUROPEAN | ISSUE DATE |            |  |                                  |  |

|-----|--------|----------|------------|------------|--|----------------------------------|--|

| IEC | JEDEC  | EIAJ     |            | PROJECTION |  | ISSUE DATE                       |  |

|     | MO-153 |          |            |            |  | <del>-95-02-10</del><br>99-12-27 |  |

| _   | IEC    |          |            |            |  | IEC JEDEC EIAJ                   |  |

28

# CK408 (66/100/133/200 MHz) spread spectrum differential system clock generator

PCK2023

### **REVISION HISTORY**

| Rev | Date     | Description                                                                                                                  |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------|

| _2  | 20030731 | Product data (9397 750 11763); ECN 853-2278 30053 dated 18 June 2003. Supersedes data of 2001 September 07 (9397 750 09142). |

|     |          | Modifications:                                                                                                               |

|     |          | <ul> <li>Minor changes or corrections to existing product specifications.</li> </ul>                                         |

| _1  | 20010907 | Product data (9397 750 09142); ECN 853-2278 27052 of 07 September 2001.                                                      |

29

## CK408 (66/100/133/200 MHz) spread spectrum differential system clock generator

PCK2023

#### **Data sheet status**

| Level | Data sheet status <sup>[1]</sup> | Product<br>status <sup>[2] [3]</sup> | Definitions                                                                                                                                                                                                                                                                                    |

|-------|----------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | Objective data                   | Development                          | This data sheet contains data from the objective specification for product development.  Philips Semiconductors reserves the right to change the specification in any manner without notice.                                                                                                   |

| II    | Preliminary data                 | Qualification                        | This data sheet contains data from the preliminary specification. Supplementary data will be published at a later date. Philips Semiconductors reserves the right to change the specification without notice, in order to improve the design and supply the best possible product.             |

| III   | Product data                     | Production                           | This data sheet contains data from the product specification. Philips Semiconductors reserves the right to make changes at any time in order to improve the design, manufacturing and supply. Relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). |

<sup>[1]</sup> Please consult the most recently issued data sheet before initiating or completing a design.

#### **Definitions**

**Short-form specification** — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 60134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

**Application information** — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### Disclaimers

Life support — These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

Right to make changes — Philips Semiconductors reserves the right to make changes in the products—including circuits, standard cells, and/or software—described or contained herein in order to improve design and/or performance. When the product is in full production (status 'Production'), relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

#### **Contact information**

For additional information please visit

http://www.semiconductors.philips.com. Fax: +31 40 27 24825

© Koninklijke Philips Electronics N.V. 2003 All rights reserved. Printed in U.S.A.

Date of release: 07-03

Document order number: 9397 750 11763

For sales offices addresses send e-mail to:

sales. addresses @www.semiconductors.philips.com.

Let's make things better.

Philips Semiconductors

<sup>[2]</sup> The product status of the device(s) described in this data sheet may have changed since this data sheet was published. The latest information is available on the Internet at URL http://www.semiconductors.philips.com.

<sup>[3]</sup> For data sheets describing multiple type numbers, the highest-level product status determines the data sheet status.